## High-frequency InAlN barrier transistors on silicon

## Researchers claim record 16GHz-µm cut-off-gate-length product for gallium nitride channel HEMTs.

niversity of Delaware in the USA claims a record for radio frequency (RF) performance of indium aluminium nitride (InAIN)-barrier gallium nitride (GaN) high-electron-mobility transistors (HEMTs) on silicon [Peng Cui et al, Appl. Phys. Express, vol12, p104001, 2019]. The device also demonstrates records for direct current (DC) characteristics such as low gate leakage, high on/off current ratio, and subthreshold swing, according to the researchers.

Usually for high performance, GaN HEMTs are produced on very expensive silicon carbide (SiC) substrates. Growth on low-cost, large-diameter silicon should open up more economic opportunities for high-power and Device fabrication included plasma reactive-ion etch of isolation mesas, and alloying of titanium/aluminium/ nickel/gold ohmic source-drain contacts at 850°C. The source-drain distance was  $2\mu m$ . The researchers used an oxygen plasma treatment to oxidize the surface between the source and drain with the aim of reducing gate leakage current (I<sub>g</sub>) and improve RF performance. The 80nm-long nickel/gold gate was centered in the source-drain gap.

The oxygen plasma treatment increased the on/off current ratio  $(I_{on}/I_{off})$  by a factor of around two to reach  $1.58 \times 10^{6}$ . Another benefit was a reduction in subthreshold swing (SS) from 76mV/decade to 65mV/decade.

high-frequency GaN-based devices.

Metal-organic chemical vapor deposition (MOCVD) on (111) resulted in an epitaxial structure with a 2µm undoped GaN buffer, a 4nm In<sub>0.12</sub>Ga<sub>0.88</sub>N backbarrier, a 15nm GaN channel, a 1nm AIN interlayer, an 8nm lattice-matched  $In_{0.17}AI_{0.83}N$ barrier, and a 2nm GaN cap. Hall measurements gave sheet electron concentration and electron mobility values in the two-dimensional electron gas (2DEG) channel of 2.28x10<sup>13</sup>/cm<sup>2</sup> respectively.

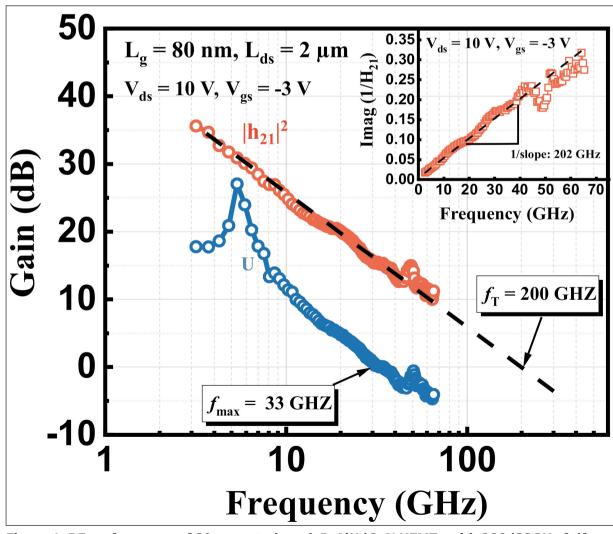

and 1205 cm<sup>2</sup>/V-s, Figure 1. RF performance of 80nm-gate-length InAlN/GaN HEMTs with 200/33GHz f<sub>T</sub>/f<sub>max</sub>. respectively. Inset: Gummel's method showing 202GHz f<sub>T</sub> estimate.

## Technology focus: III-Vs on silicon 63

The team comments: "To the best of our knowledge, these DC measurement results all show record values among those reported InAIN/GaN HEMTs on silicon to-date ( $I_g$  of  $7x10^{-6}$ A/mm,  $I_{off}$  of  $7x10^{-6}$ A/mm,  $I_{off}$  of  $7x10^{-6}$ A/mm,  $I_{off}$  of  $7x10^{-6}$ A/mm,  $I_{off}$  of 82mV/decade are the best values that have been reported in InAIN/GaN HEMTs)."

The researchers admit that better values have been obtained for  $I_g$  and  $I_{off}$  with 20nm aluminium gallium nitride (AlGaN) barrier HEMTs on silicon — of order  $10^{-12}$ A/mm for both. The resulting  $I_{on}/I_{off}$  was 2.5x10<sup>11</sup>.

However, one benefit of the thinner InAlN-based barrier was better electrostatic control of current flow in the channel, reducing shortchannel effects (SCEs). The InGaN back barrier reduces losses from current leaking into the buffer layer and improves confinement of charge carriers to the GaN-channel region.

The peak transconductance of the InAIN-HEMT <<100nm." was 391mS/mm with 10V drain bias, beating a 75nm-gate 11.4nmbarrrier AlGaN-HEMT's 374mS/mm that has been reported. An 80nm-gate AIN-HEMT on silicon has been presented with 580mS/mm peak transconductance, enabled by a very thin 6nm barrier. SiC/Si with <<100nm." Using an em model that r f<sub>T</sub> to L<sub>g</sub>, barr thickness, the one fitting p the research project that of 546GHz c

The 1.26A/mm maximum drain current of the team's InAIN-HEMT has also been bettered by a

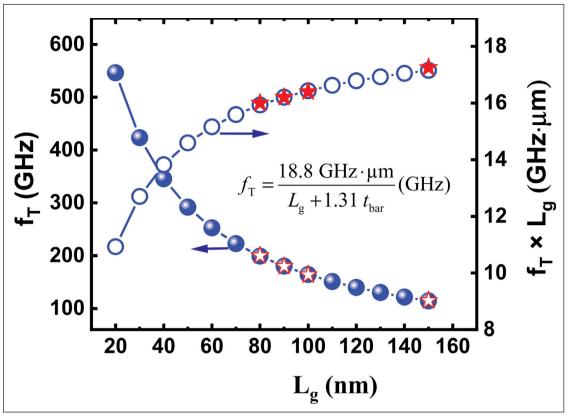

Figure 2. Predicted  $f_T$  (left) and  $f_TxL_g$  (right) as a function of  $L_g$  — stars represent experimental results.

The team comments: "To the best of our knowledge, the f<sub>T</sub>xL<sub>g</sub> in our study achieves the highest value among all reported GaN HEMTs on silicon, and set a new record among GaN HEMTs on SiC/Si with L<sub>g</sub> <<100nm."

Using an empirical model that relates  $f_T$  to  $L_{gr}$  barrier thickness, the effective electron velocity and one fitting parameter, the researchers project that an  $f_T$ of 546GHz could be achieved with 20nm  $L_{gr}$  giving a  $f_TxL_g$  value of 10.9GHz-um similar device on silicon with a very small 300nm source-drain gap (2.66A/mm). The wider  $2\mu$ m gap of the team's HEMT naturally increased the on-resistance. One would expect, although the paper does not report on this, that the wider gap would lead to a higher breakdown voltage performance.

RF measurements were made in the 1–65GHz range (Figure 1). With parasitic elements accounted for ('de-embedded'), the current gain cut-off ( $f_T$ ) was extracted as 200GHz, using a –20dB/decade extrapolation. The drain bias was 10V and the gate potential was set at –3V. The maximum oscillation/power gain ( $f_{max}$ ) was 33GHz, suffering due to losses from the high resistance of the rectangular gate.

The cut-off-gate-length product ( $f_TxL_g$ ) was 16GHz- $\mu m$ . The researchers compare this with best result obtained on SiC - 17.8GHz- $\mu m$  from 162GHz  $f_T$  and 110nm  $L_g$ . The team comments: "To the best of our knowledge, the  $f_TxL_g$  in our study achieves the highest value among all reported GaN HEMTs on silicon, and set a new record among GaN HEMTs on SiC/Si with  $L_g$  <<100nm."

Using an empirical model that relates  $f_T$  to  $L_g$ , barrier thickness, the effective electron velocity and one fitting parameter, the researchers project that an  $f_T$  of 546GHz could be achieved with 20nm  $L_g$ , giving a  $f_TxL_g$  value of 10.9GHz-µm (Figure 2). https://iopscience.iop.org/article/10.7567/ 1882-0786/ab3e29

Author: Mike Cooke