# Imec develops 200V & 650V dispersion-free normally-off/ **E-mode GaN power devices** on 200mm silicon

#### **Technology ready for** prototyping, customized lowvolume production and technology transfer.

anoelectronics and photovoltaics research centre Imec of Leuven, Belgium has developed 200V and 650V normally-off/enhancement mode (E-mode) on 200mm/8-inch gallium nitride on silicon (GaN-on-Si) wafers, achieving a very low dynamic Ron dispersion (below 20%) and what is claimed to be state-ofthe-art performance and reproducibility. Stress tests have also shown good device reliability, it adds. Imec's technology is ready for prototyping, customized low-volume production and technology transfer.

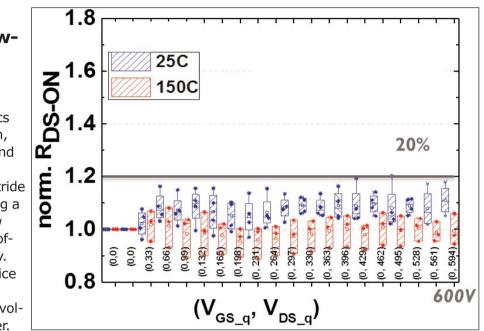

Dynamic R<sub>DS-ON</sub> dispersion (10µs on – 90µs off) of Imec's 650V

GaN technology offers faster-switching power devices with higher breakdown volt- GaN-on-Si E-mode device technology measured at 25°C and 150°C.

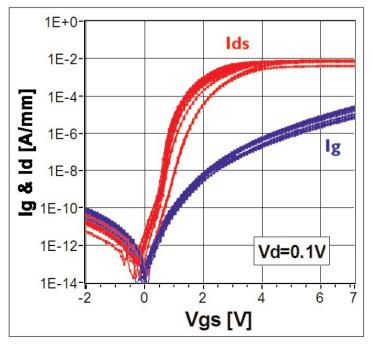

Transfer characteristic of 36mm gate width imec's 650V GaN-on-Si e-mode transistors.

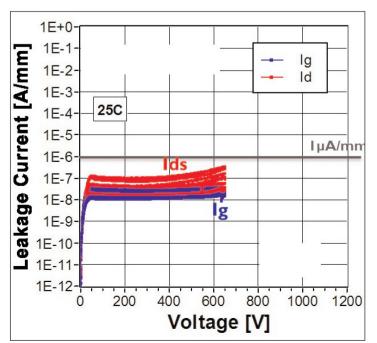

Leakage characteristic at V<sub>GS</sub>=0V of 36mm gate width imec's 650V GaN-on-Si e-mode transistors.

#### Technology focus: III-Vs on silicon 99

| Parameter                                            | Symbol                  | Value | Unit  | Conditions                                                                    |

|------------------------------------------------------|-------------------------|-------|-------|-------------------------------------------------------------------------------|

| Drain-to-Source BreakdownVoltage (Min.)              | BV <sub>DSS</sub>       | 200   | V     | V <sub>GS</sub> = 0V                                                          |

| Drain-to-Source On Resistance (25 °C)                |                         | 7     | Ω∙mm  | $V_{DS} = 0.1V, V_{GS} = V_{GS(th)@max-gm} + 4V, 25 \ ^{\circ}C$              |

| Drain-to-Source On Resistance (150 °C)               | - R <sub>DS(ON)</sub>   | 12    | Ω∙mm  | V <sub>DS</sub> = 0.1V,V <sub>GS</sub> =V <sub>GS(th)@max-gm</sub> +4V,150 °C |

| Dynamic Drain-to-Source On Resistance<br>(RT/150 °C) | R <sub>DS(ON)-DYN</sub> | < 20  | %     | From off-state 10 µs on, 90 µs off                                            |

| Gate Threshold Voltage                               | V <sub>GS(th)</sub>     | 1.3   | V     | $I_D = 10 \mu A/mm and V_{DS} = V_{GS}$                                       |

|                                                      |                         | 2.4   | V     | at max-gm                                                                     |

| Drain Leakage Current (25 °C)                        |                         | < 10  | nA/mm | V <sub>DS</sub> =200V,V <sub>GS</sub> =0V,25 °C                               |

| Drain Leakage Current (150 °C)                       | - I <sub>DSS</sub>      | <     | µA/mm | V <sub>DS</sub> =200V,V <sub>GS</sub> =0V, I 50 °C                            |

| Gate-to-Source Voltage                               | V <sub>GS</sub>         | >4.5  | V     | I <sub>GS</sub> =IµA/mm                                                       |

| Gate-to-Source Current                               | I <sub>GS</sub>         | < 10  | µA/mm | V <sub>DS</sub> =0V,V <sub>GS</sub> =6V                                       |

Normalized spec table of imec's 200V GaN-on-Si e-mode device technology.

| Parameter                                            | Symbol                  | Value | Unit  | Conditions                                                                  |

|------------------------------------------------------|-------------------------|-------|-------|-----------------------------------------------------------------------------|

| Drain-to-Source BreakdownVoltage (Min.)              | BV <sub>DSS</sub>       | 650   | V     | V <sub>GS</sub> = 0V                                                        |

| Drain-to-Source On Resistance (25 °C)                | - R <sub>DS(ON)</sub>   | 13    | Ω∙mm  | V <sub>DS</sub> = IV,V <sub>GS</sub> =V <sub>GS(th)@max-gm</sub> +4V,25 °C  |

| Drain-to-Source On Resistance (150 °C)               |                         | 28    | Ω∙mm  | V <sub>DS</sub> = IV,V <sub>GS</sub> =V <sub>GS(th)@max-gm</sub> +4V,I50 °C |

| Dynamic Drain-to-Source On Resistance<br>(RT/150 °C) | R <sub>DS(ON)-DYN</sub> | < 20  | %     | From off-state 10 µs on, 90 µs off                                          |

| Gate Threshold Voltage                               | V <sub>GS(th)</sub>     | 1.1   | V     | $I_D = 10 \mu A/mm and V_{DS} = V_{GS}$                                     |

|                                                      |                         | 2.1   | v     | at max-gm                                                                   |

| Drain Leakage Current (25 °C)                        | - I <sub>DSS</sub>      | < 200 | nA/mm | V <sub>DS</sub> =650V,V <sub>GS</sub> =0V,25 °C                             |

| Drain Leakage Current (150 °C)                       |                         | < 10  | µA/mm | V <sub>DS</sub> =650V,V <sub>GS</sub> =0V, I 50 °C                          |

| Gate-to-Source Voltage                               | V <sub>GS</sub>         | > 4   | V     | I <sub>GS</sub> =IµA/mm                                                     |

| Gate-to-Source Current                               | I <sub>GS</sub>         | < 10  | µA/mm | V <sub>DS</sub> =0V,V <sub>GS</sub> =6V                                     |

Normalized spec table of imec's 650V GaN-on-Si e-mode device technology.

age and lower on-resistance than silicon, making it a suitable material for advanced power electronic components. Imec says that its GaN-on-Si device technology is gold (Au)-free and compatible with the wafer handling and contamination requirements for processing in a silicon fabrication plant.

A key component of the GaN device structure is the buffer layer, which is required to accommodate the large difference in lattice parameters and thermal expansion coefficient between the AlGaN/GaN materials system and the silicon substrate. Imec has developed a patent pending buffer design that allows growth of buffers qualified for 650V on large-diameter 200mm wafers. This, in combination with the choice of the silicon substrate thickness and doping, increased the GaN substrate yield on 200mm to competitive levels, enabling low-cost production of GaN power devices, says Imec.

In addition, the cleaning and dielectric deposition conditions have been optimized, and the field plate design (a common technique for achieving performance improvement) has been studied extensively. As a result, the devices exhibit dynamic  $R_{on}$  dispersion below 20% up to 650V over the full temperature range of 25–150°C. This means that there is almost no change in the transistor on-state after switching from the off-state (a challenge typical for GaN technology).

"Having pioneered the development of GaN-on-Si power device technology on large-diameter substrates (200mm/8-inch), Imec now offers companies access to its normally-off/e-mode GaN power device technology through prototyping, low-volume manufacturing as

### 100 Technology focus: III-Vs on silicon

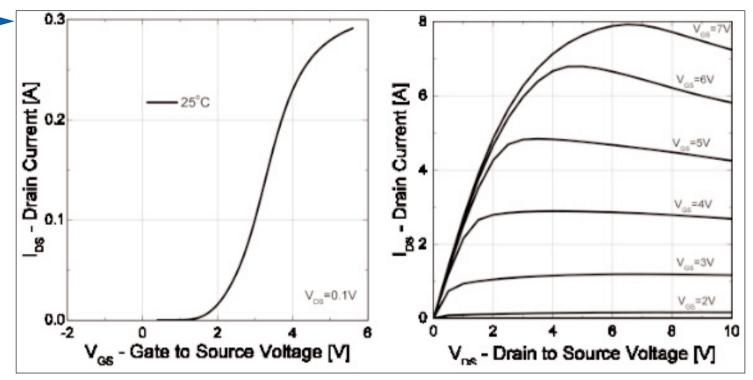

Typical output characteristic and transfer characteristic of 36mm-gate-width 650V GaN-on-Si e-mode device technology.

well as via a full technology transfer," says Stefaan Decoutere, Imec's program director for GaN technology. "Next to enhancement-mode power device switches, Imec also provides lateral Schottky diodes for power switching applications," he adds. "Based on Imec's proprietary device architecture, the diode combines low turn-on voltage with low leakage current, up to 650V a combination that is very challenging to achieve."

200mm/8-inch GaN-on-Si normallyoff/e-mode Au free processed wafer.

## REGISTER for Semiconductor Today free at www.semiconductor-today.com