# Reaching new heights by producing 1200V SiC MOSFETs in CMOS fab

**Monolith Semiconductor** and **Littelfuse** describe how 1200V silicon carbide MOSFETs can be mass produced on 150mm wafers in a CMOS silicon fab.

he emergence of silicon carbide (SiC) power devices has brought the advantages of high-speed unipolar devices into much higher-voltage classes than would be achievable with silicon devices. SiC metal-oxide-semiconductor field-effect transistors (MOSFETs) demonstrate dramatically lower switching losses than similarly rated silicon IGBTs.

The very first commercial SiC MOSFETs rated at 1200V were introduced to the market back in January 2011 [1]. Since then, a growing number of power electronics systems manufacturers have turned to subsequent generations of these devices in order to achieve greater efficiency, power density, and reliability at a lower cost. However, in order for these devices to reach their commercial potential, providing a high-performance, near-ideal switch is not enough to ensure the widespread adoption of these devices. SiC MOSFET manufacturers also must be able to offer their power electronics customers' devices that combine good manufacturability, long-term reliability, and exceptional ruggedness, all at a competitive price (Figure 1).

One approach to reaching this goal is to move from 76mm (3-inch)- and 100mm (4-inch)diameter SiC wafers to 150mm (6-inch) SiC wafers and develop design and process techniques that are compatible with processes in a CMOS fab. Integrating the process flows for both silicon and SiC wafers and running them in parallel allows one to take advantage of enormous economies of scale. The results of this approach, employed recently in the production of 1200V SiC MOSFETs in an automotivequalified 150mm CMOS fab, have demonstrated not only high manufacturability but also superior device performance, gate oxide reliability and robustness at operating junction temperatures of 175°C.

performance, near-ideal switch is not enough to ensure the widespread adoption of these **Figure 1. Widespread adoption of high-voltage SiC MOSFETs will require much more than just high-performance devices.**

# Silicon carbide fabrication processes and device design

More than 90% of SiC device processes are compatible with processes already in use in silicon CMOS fabs. Although the nature of SiC as a material makes it fundamentally compatible with most CMOS fab processes, significant hurdles remain before this approach can be realized, including requirements for high-temperature processing. Other challenges include integrating CMOS- and SiC-specific process steps, as well as making metal and dielectric stacks used in the SiC MOSFET compatible with a conventional CMOS fab. Whenever possible, standard process steps available in a CMOS foundry should be reused with SiC wafers, such as implantation masks and top-level interconnects.

For steps such as gate oxidation and metallization, SiC-specific processes can be developed using CMOS production tools like high-temperature furnaces and rapid thermal processing (RTP) ovens, but dedicated tools are required for implant activation and certain ion implantation steps. It's also necessary to modify the mechanical wafer handling methods used because of the semi-transparent nature of SiC wafers. For example, sensors set up for use with opaque materials will respond incorrectly when used with SiC wafers, leading to wafer breakage during loading/unloading .Similarly, automated defect detection tools can confuse sub-surface features with surface defects. Differences in wafer thickness can also complicate wafer handling. Nevertheless, with the proper process modifications, SiC and silicon wafers can be run in parallel in a high-volume production environment, taking advantage of the economies of scale associated with the production processes already in place in the CMOS fab.

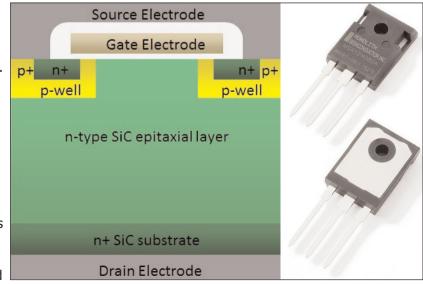

Producing rugged SiC MOSFETs (see Figure 2) with wide process margins demands ensuring stable and uniform avalanche breakdown in the device unit cells, avoiding high fields in the oxide, and breakdown in the edge termination. Ideally, device termination should achieve close-to-ideal parallel plane breakdown voltage over a broad dose range, providing a wide process margin.

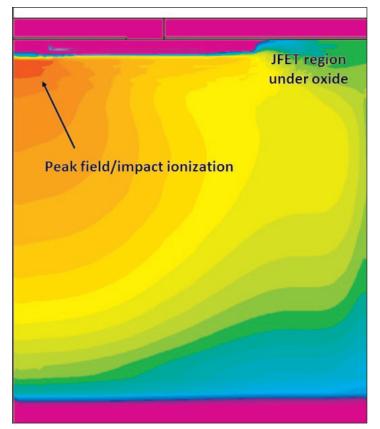

In addition to the device termination, the JFET region of the device under oxide must be optimized with appropriate doping concentration and physical dimensions. Figure 3 illustrates an example of impact ionization contours at device breakdown. In this case, the device was designed to preferentially break down at the center of the unit cell, ensuring uniform avalanche conditions and a low peak field in the oxide. Other critical aspects of the device and process design included optimization of the channel and P-well designs to ensure the device remained off over the entire voltage and temperature envelope.

Figure 3. Impact ionization contours at device breakdown. The device was designed to break down at the center of the unit cell, ensuring stable avalanche breakdown.

#### **Performance of fabricated devices**

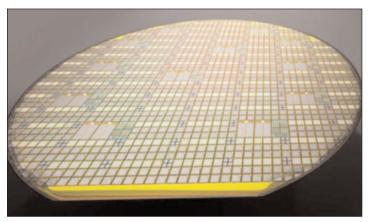

Figure 4 shows a fully processed 150mm SiC wafer with 1.2kV, 65mΩ MOSFETs fabricated in an automotive-qualified fab using the process outlined in this article. Multiple wafer lots have been produced with various process and design splits. The devices produced have been thoroughly characterized at both the wafer level and in TO-247 packages. Wafer-level results have been used to generate wafer maps and gain an understanding of various process-design interactions. Packaged parts are used for final reliability and ruggedness evaluations.

Figure 4. Fully processed 150mm SiC wafer with 1.2kV MOSFETs and process control monitors.

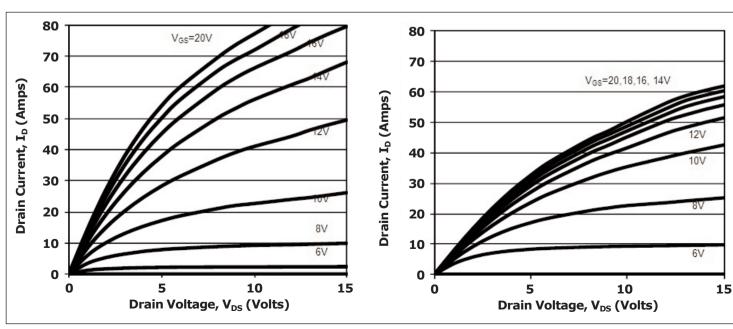

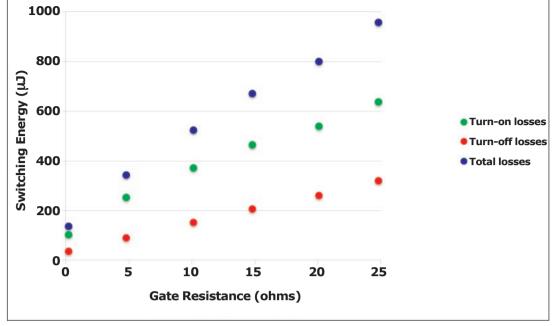

manufacturability, the typical specific on-resistance R<sub>sp</sub> (normalized to the devices' active area) is competitive with that of other commercially available 1200V SIC MOSFETs. With more aggressive processes and designs, it has proven possible to achieve R<sub>sp</sub> of  $3.1 \text{m}\Omega\text{-cm}^2$  on an identical process platform. Figure 7 details the SiC MOSFET's low switching losses when 800V, 20A.

Switching loss at

robustness and

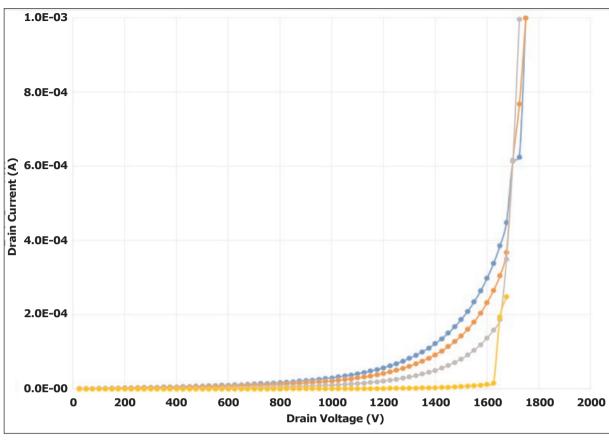

Figure 5. Typical forward characteristics ( $I_{DSS}$ ;  $V_{GS} = 0$ ) of manufactured MOSFETs for temp-characterized ateratures from 25°C to 175°C. Results show low leakage current up to 1200V and 175°C.800V, 20A.Current up to 1200V and 175°C.

Figure 5 presents the typical off-state IV (V<sub>GS</sub> = 0) characteristics of the fabricated MOSFETs from 25°C to 175°C with low leakage current (<100µA) over a worst-case voltage and temperature envelope.

Figure 6 compares the forward characteristics of these devices at 25°C and 175°C. The typical on-resistance of these MOSFETs at  $V_{GS}$  = 20V, 25°C is 65m $\Omega$ . Although these devices were optimized for

a gate resistance of  $4.8\Omega$  was under  $400\mu$ J, indicating superior switching performance.

Controlling SiC MOSFET production costs effectively

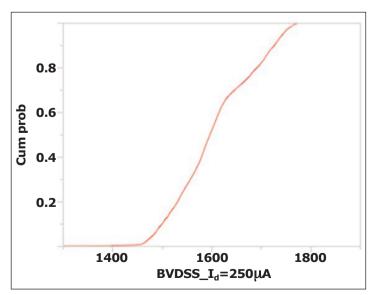

we analyzed the breakdown voltage distribution of a

demands a highly manufacturable process with sufficient

margin. To evaluate the manufacturability of this process,

#### **Evaluating device manufacturability**

Figure 6. Forward characteristics at 25°C (left) and 175°C (right).

semiconductorTODAY Compounds&AdvancedSilicon • Vol. 11 • Issue 6 • July/August 2016

#### Figure 7. The devices exhibited less than $400\mu$ J of switching loss at a gate resistance of $4.8\Omega$ .

large quantity of devices from multiple wafers from different fab lots (Figure 8). This analysis showed that the process offers sufficient margin to accommodate a wide range of epilayer doping variations.

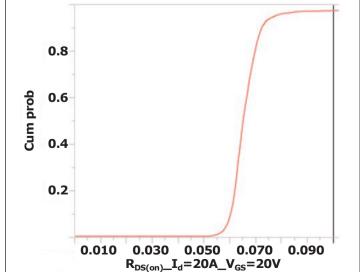

As part of our manufacturability analysis, we also analyzed R<sub>DS(on)</sub> or on-resistance (Figure 9). Note that the on-resistance distribution is quite tight

despite the epitaxial layer doping variation.

Given that 150mm SiC wafers are not yet as common as 100mm SiC wafers, the diode leakage current of the fabricated devices was also investigated to assess defect density and device yields. Diode leakage wafer maps revealed only randomly located failures and >90% yields, which eliminated any concerns about the quality of 150mm wafers affecting device yields. Work on improving the epitaxial doping control aspect of the process continues. Doping variation has been taken into account in these designs and it is reflected in the wide breakdown voltage margin.

#### Assessing device ruggedness and reliability

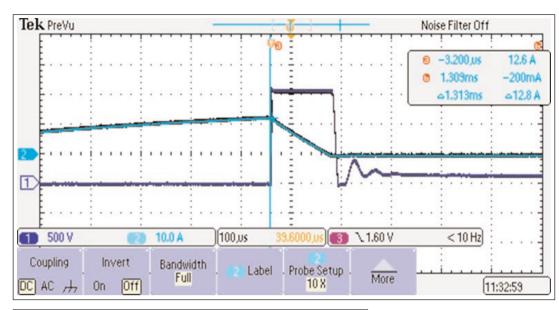

A number of techniques were used to evaluate the ruggedness of the devices produced, including the avalanche energy of the device. Figure 10 shows the typi-

cal waveform from avalanche energy characterization of the device with an avalanche energy >1 Joule.

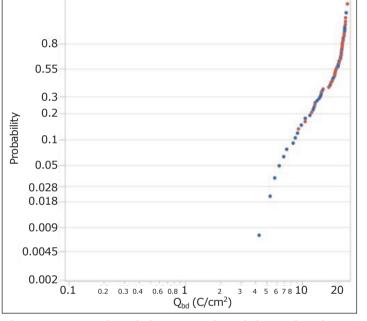

Because gate oxide quality is a common concern for SiC MOSFETs, the fundamental quality of the gate oxide process was studied previously using time-dependent dielectric breakdown (TDDB) measurement of capacitors at high temperatures [2]. Charge-to-breakdown ( $Q_{BD}$ ) measurements in large-area DMOSFETs produced  $Q_{BD}$ values that were well above 10C/cm<sup>2</sup> (see Figure 11) and no defective tail that would indicate intrinsic failure modes. High-temperature gate bias (HTGB) testing at  $V_{GS}$  of -10V and +20V showed excellent stability of threshold voltage, as presented in [3]. The MOSFETs were also subjected to 1400 hours of high-temperature (175°C) reverse bias (HTRB) testing at  $V_{DS}$  = 960V and  $V_{GS}$  = 0V, and stable breakdown voltage characteristics were observed.

Figure 8. Breakdown voltage distribution of a large quantity of devices from multiple wafers from different fab lots.

Figure 9. On-resistance distribution of a large quantity of devices from multiple wafers from different fab lots.

#### Figure 10. Avalanche energy characterization of the SiC MOSFETs, showing avalanche energy > 1 Joule.

2011/January/110117-MOSFET, 17 January 2011. [2] Z. Chbili et al, 'Time Dependent Dielectric Breakdown in High Quality SiC MOS Capacitors', Materials Science Forum, vol. 858, pp615–618, 2016. [3]K. Matocha, S. Banerjee, K. Chatty, 'Advanced SiC Power MOSFETS Manufactured on 150mm SiC Wafers', Materials Science Forum, vol. 858, pp803–806, 2016. [4] S. Banerjee et al, 'Manufacturable and Rugged 1.2 KV SiC

MOSFETs Fabricated in High-Volume 150mm CMOS Fab', International Symposium on Power Semiconductor Devices & ICs, 2016, Prague, Czech Republic.

#### Acknowledgements

The authors gratefully acknowledge the support received from the US Advanced Research Projects Agency-Energy (ARPA-E) Strategies for Wide Bandgap, Inexpensive Transistors for Controlling High-Efficiency Systems (SWITCHES) program (contract DE-AR0000442), the US Army Research Lab (contracts W911F-14-2-0112 and W911NF-15-2-0088), and the US Department of Energy and PowerAmerica (for SiC fab funding).

#### Authors:

**Sujit Banerjee** is CEO & founder of Monolith Semiconductor Inc, which focuses on commercializing and enabling widespread adoption of SiC power semiconductors. He holds a PhD from Rensselaer Polytechnic Institute (RPI), and has been awarded more than 25 patents for his work in power semiconductors.

**Kevin Matocha**, Monolith Semiconductor's president & co-founder, holds a PhD from RPI. Previously, at the General Electric Global Research Center, he developed wide-bandgap devices, including harsh-environment sensors and power devices using silicon carbide and gallium nitride. He helped to commercialize SiC power devices, including high-voltage SiC Schottky diodes and SiC JFETs as VP of product development at SemiSouth.

*Kiran Chatty*, Monolith Semiconductor's VP of product development & co-founder, holds a PhD from RPI and has been awarded more than 40 patents and has published more than 50 articles.

**Kevin Speer** joined Littelfuse in January 2015 as the business development manager responsible for providing strategic direction for the growth of the company's power semiconductor business. He holds a BSEE from the University of Arkansas, and an M. Eng. and a PhD from Case Western Reserve University.

# Figure 11. Results of charge-to-breakdown (Q<sub>BD</sub>) measurements in large-area DMOSFETs.

#### Conclusion

In the coming years, the average selling price of commercial 1200V SiC MOSFETS is likely to continue to decrease, from the present price of ~50 cents/amp to somewhere around 10 cents/amp by the end of the decade. However, in order to achieve this price point and allow for widespread adoption of SiC power MOSFETs, suppliers must continue to explore opportunities to lower their costs without compromising device quality. Producing these devices in high-volume, automotivequalified 150mm CMOS fabs has proven to be one way to achieve this goal [4]. ■

#### References

[1]Cree Inc, 'Cree Launches Industry's First Commercial Silicon Carbide Power MOSFET; Destined to Replace Silicon Devices in High-Voltage (≥ 1200-V) Power Electronics', www.cree.com/News-and-Events/Cree-News/Press-Releases/

# Choose Semiconductor Today for ...

## MAGAZINE

semiconductor TODA

Accurate and timely coverage of the compound semiconductor and advanced silicon industries

Targeted 41,000+ international circulation

Published 10 times a year and delivered by e-mail and RSS feeds

# **WEB SITE**

Average of over 19,700 unique visitors to the site each month

Daily news updates and regular feature articles

Google-listed news source

# E-BRIEF

Weekly round-up of key business and technical news

E-mail delivery to entire circulation

Banner and text marketing opportunities available

# www.semiconductor-today.com

**in** Join our LinkedIn group: Semiconductor Today

Follow us on Twitter: Semiconductor\_T