## High-frequency nitride HEMTs on silicon with high breakdown

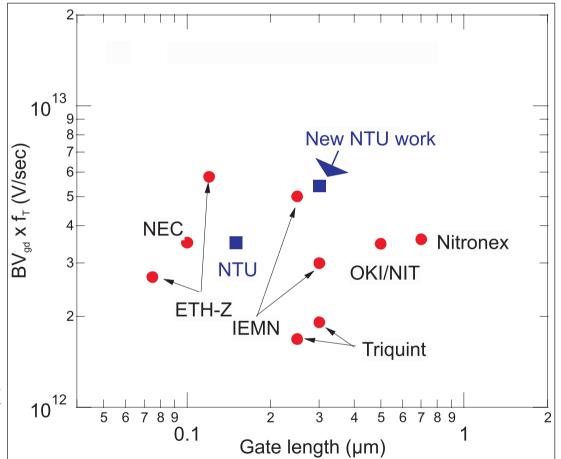

Highest breakdown cut-off product for 0.3µm T-gate conventional SiN passivated transistors without field plates.

ingapore's Nanyang Technological University (NTU) has developed a passivation process for aluminium gallium nitride on gallium nitride (AlGaN/GaN) high-electron-mobility transistors (HEMTs) on silicon substrates that significantly improves breakdown voltage without impacting frequency performance [S. Arulkumaran et al, IEEE Electron Device Letters, 16 September 2013].

The Johnson figure of merit combining breakdown voltage and cut-off frequency ( $BV_{gd} \ge T_T$ ) was 5.41  $\ge 10^{12}$ V/sec (Figure 1, Table 1), "which is the highest value reported so far for 0.3µm T-gate conventional SiN passivated AlGaN/GaN HEMTs on Si substrate without additional  $\Gamma$ -gate and/or source field plate."

Figure 1. State-of-the-art Johnson figures of merit versus gate lengths for AIGaN/GaN HEMTs on silicon substrates.

| Table 1. State-of-the-art $f_T$ and $BV_{gd}$ for conventional AlGaN/GaN HEMTS on Si. |                      |                      |                                                           |                      |                       |  |

|---------------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------------------------------------|----------------------|-----------------------|--|

| Affiliation                                                                           | f <sub>⊤</sub> (GHz) | BV <sub>gd</sub> (V) | BV <sub>gd</sub> x f <sub>T</sub> (x10 <sup>12</sup> V/s) | Gate type            | Passivation           |  |

| IEMN                                                                                  | 50.0                 | 100                  | 5.00                                                      | T-gate               | SiO <sub>2</sub> /SiN |  |

| OKI/NIT                                                                               | 13.9                 | 250                  | 3.48                                                      | $\Gamma$ -gate & SFP | SiN                   |  |

| ETH-Z                                                                                 | 100.0                | 58                   | 5.80                                                      | T-gate               | SiN                   |  |

| NTU                                                                                   | 39.0                 | 90                   | 3.51                                                      | T-gate (non-gold)    | SiN                   |  |

| Triquint                                                                              | 24.0                 | 70                   | 1.68                                                      | T-gate & SFP         | SiN                   |  |

| Nitronex                                                                              | 18.0                 | 200                  | 3.60                                                      | Γ-gate & SFP         | SiN                   |  |

| NEC                                                                                   | 60.0                 | 55                   | 3.30                                                      | T-gate               | SiN                   |  |

| NTU treated HEMT                                                                      | 34.0                 | 159                  | 5.41                                                      | T-gate               | $[(NH_4)_2Sx] + SiN$  |  |

## Technology focus: Nitride transistors **91**

The AIGaN/GaN semiconductor layers (Figure 2) were applied to 4-inch high-resistivity (more than  $6000\Omega$ -cm) silicon substrates using metal-organic chemical vapor deposition (MOCVD). The mobility and carrier density of the two-dimensional electron gas (2DEG) channel were 1455cm<sup>2</sup>/V-s and 9.6x10<sup>12</sup>/cm<sup>2</sup>, respectively.

Transistor fabrication began with plasma etch of the mesa isolation, and application and annealing of titanium/ aluminium/nickel/gold ohmic source-drain electrodes.

Preparation for the silicon nitride passivation consisted of a 1-minute buffer hydrofluoric acid dip, and an ammonium sulfide ( $(NH_4)_2S_x$ ) surface treatment at 50°C for 15 minutes. The silicon nitride was applied in a 50nm layer using plasma-enhanced chemical vapor deposition (PECVD at 300°C).

Gate formation consisted of electron-beam patterning and silicon nitride etch. The gate footprint was 0.3µm and the gate head was 0.7µm. The gate stack consisted of 50nm of nickel and 400nm of gold.

Final processing consisted of adding titanium/gold (50nm/1000nm) transmission lines and further passivation with 150nm of PECVD silicon nitride.

Comparison devices were also produced without the  $(NH_4)_2S_x$ ) surface treatment.

646mA/mm, compared with 636mA/mm for the untreated HEMT. The respective peak extrinsic transconductances were 175mS/mm and 205mS/mm. A real difference in performance is seen in the on/off current ratios, which are three orders of magnitude higher in the treated HEMT.

Another improvement is the much lower subthreshold swing of the treated device: 77mV/decade, compared with 112mV/dec for the untreated device. The researchers consider the low subthreshold swing to be evidence of low interface trap densities as a result of the (NH<sub>4</sub>)<sub>2</sub>Sx surface treatment.

A further benefit of treatment is a six-fold increase in gate-drain breakdown voltage (BV<sub>ad</sub> for drain current 0.5mA/mm) to 159V. The higher breakdown voltage was achieved while maintaining a cut-off frequency  $(f_T)$  of 34GHz and maximum oscillation (f<sub>max</sub>) of 52GHz.

| Сар        | GaN           | 2nm    |

|------------|---------------|--------|

| Barrier    | A10.26Ga0.74N | 18nm   |

| Channel    | GaN           | 800nm  |

| Buffer     | GaN           | 1400nm |

| Nucleatior | AIN           | 100nm  |

| Substrate  | Si (111)      |        |

Figure 2. Schematic structure of nitride semiconductor epitaxy on silicon for HEMT.

$(f_T x L_a)$  was 10.2GHz-µm, a little smaller than the best value of 12.5GHz-µm reported in 2005 by Lille University.

The researchers found that the improved breakdown performance is linked to three orders of magnitude lower surface current leakage in the treated devices by passivation of dangling bonds and interface traps between GaN and SiN.

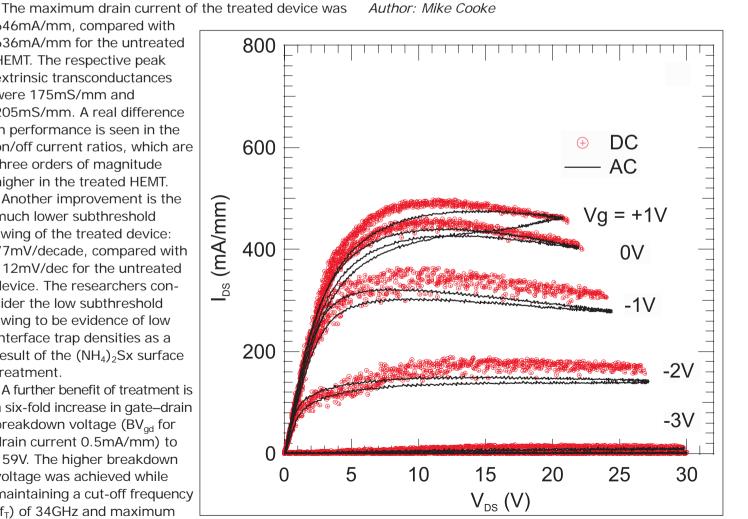

The researchers also carried out 100Hz AC measurements, which showed "no significant drain current collapse" (Figure 3). ■

http://ieeexplore.ieee.org/xpl/articleDetails.jsp ?arnumber=6600863 Author: Mike Cooke

Figure 3. DC and AC (100Hz) drain current versus drain voltage characteristics The cut-off gate-length product of AlGaN/GaN HEMTs ( $L_{sg}/W_g/L_g/L_{gd} = 1.0/(2x100)/0.3/3.0\mu m$ ).